## A charge inverter for III-nitride light-emitting diodes

Zi-Hui Zhang, Yonghui Zhang, Wengang Bi, Chong Geng, Shu Xu, Hilmi Volkan Demir, and Xiao Wei Sun

Citation: Applied Physics Letters **108**, 133502 (2016); doi: 10.1063/1.4945257 View online: http://dx.doi.org/10.1063/1.4945257 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/108/13?ver=pdfcov Published by the AIP Publishing

Articles you may be interested in

III-nitride light-emitting diode with embedded photonic crystals Appl. Phys. Lett. **102**, 181117 (2013); 10.1063/1.4804678

Defect-related tunneling mechanism of efficiency droop in III-nitride light-emitting diodes Appl. Phys. Lett. **96**, 133502 (2010); 10.1063/1.3367897

Carrier recombination mechanisms in nitride single quantum well light-emitting diodes revealed by photo- and electroluminescence J. Appl. Phys. **104**, 094504 (2008); 10.1063/1.3009335

Polarization of III-nitride blue and ultraviolet light-emitting diodes Appl. Phys. Lett. **86**, 091107 (2005); 10.1063/1.1875751

Carrier dynamics in nitride-based light-emitting p-n junction diodes with two active regions emitting at different wavelengths

J. Appl. Phys. 94, 2167 (2003); 10.1063/1.1591051

## A charge inverter for III-nitride light-emitting diodes

Zi-Hui Zhang,<sup>1,a)</sup> Yonghui Zhang,<sup>1</sup> Wengang Bi,<sup>1,a)</sup> Chong Geng,<sup>1</sup> Shu Xu,<sup>1</sup> Hilmi Volkan Demir,<sup>2,3,a)</sup> and Xiao Wei Sun<sup>2,4,a)</sup>

<sup>1</sup>Key Laboratory of Electronic Materials and Devices of Tianjin, School of Electronics and Information Engineering, Hebei University of Technology, 5340 Xiping Road, Beichen District, Tianjin 300401, People's Republic of China

<sup>2</sup>LUMINOUS! Centre of Excellence for Semiconductor Lighting and Displays, School of Electrical and Electronic Engineering, Nanyang Technological University, 50 Nanyang Avenue, 639798 Singapore

<sup>3</sup>Department of Electrical and Electronics, Department of Physics, and UNAM-Institute of Material Science and Nanotechnology, Bilkent University, TR-06800 Ankara, Turkey

<sup>4</sup>Department of Electrical and Electronic Engineering, College of Engineering, South University of Science

and Technology, 1088 Xue-Yuan Road, Nanshan, Shenzhen, Guangdong 518055, People's Republic of China

(Received 12 January 2016; accepted 20 March 2016; published online 30 March 2016)

In this work, we propose a charge inverter that substantially increases the hole injection efficiency for InGaN/GaN light-emitting diodes (LEDs). The charge inverter consists of a metal/electrode, an insulator, and a semiconductor, making an Electrode-Insulator-Semiconductor (EIS) structure, which is formed by depositing an extremely thin SiO<sub>2</sub> insulator layer on the p<sup>+</sup>-GaN surface of a LED structure before growing the p-electrode. When the LED is forward-biased, a weak inversion layer can be obtained at the interface between the p<sup>+</sup>-GaN and SiO<sub>2</sub> insulator. The weak inversion region can shorten the carrier tunnel distance. Meanwhile, the smaller dielectric constant of the thin SiO<sub>2</sub> layer increases the local electric field within the tunnel region, and this is effective in promoting the hole transport from the p-electrode into the p<sup>+</sup>-GaN layer. Due to the improved hole injection, the external quantum efficiency is increased by 20% at 20 mA for the 350 × 350  $\mu$ m<sup>2</sup> LED chip. Thus, the proposed EIS holds great promise for high efficiency LEDs. © 2016 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4945257]

Replacing incandescent and fluorescent light sources, III-nitride based light-emitting diodes (LEDs) are expected to make significant contribution in relieving the global warming effect as a result of their energy saving feature if used at world scale.<sup>1</sup> However, in order to increase the saving in energy consumption and the scale of their use, there is room for further boosting their external quantum efficiency (EQE). One of the bottlenecks that hinder further enhancement of the quantum efficiency for III-nitride LEDs is the limited hole injection into the quantum wells.<sup>2</sup> The hole injection efficiency into the multiple quantum wells (MQWs) is affected by various factors, including the inhomogeneous hole concentration in the quantum wells, the blocking effect caused by the p-electron blocking layer (p-EBL), and the hole transport from the p-electrode to the  $p^+$ -GaN region. The non-uniform hole distribution that often takes place in the MQWs leads to a strong hole accumulation in the quantum wells close to the p-GaN side.<sup>3</sup> The hole injection can be homogenized by doping the quantum barriers with Mg acceptors,<sup>4,5</sup> using the InGaN instead of the GaN as the quantum barriers,<sup>6</sup> properly reducing the quantum barrier thickness,<sup>7</sup> increasing the thickness of the quantum well close to the p-GaN layer<sup>8</sup> and/or employing the cascaded active region.<sup>9</sup> As is well known, the p-EBL is adopted in the III-nitride LEDs to reduce the electron leakage, which nevertheless also blocks the hole injection due to the band offset between the p-EBL and the subsequent p-GaN layer.<sup>10</sup> Therefore, different p-EBL structures have been reported to increase the hole injection, such as the

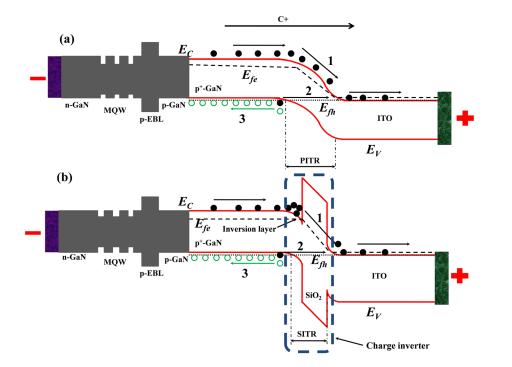

The physical mechanism of the proposed charge inverter for promoting the hole injection from the p-electrode into the  $p^+$ -GaN layer is illustrated in Fig. 1. We use ITO as the current spreading layer, which is a heavily doped n-type semiconductor. For device A in Fig. 1(a) that does not have the charge inverter, the  $p^+$ -GaN/ITO behaves as the  $p^+$ -GaN/

stanfordalumni.org; and sunxw@sustc.edu.cn

<sup>a)</sup>Electronic addresses: zh.zhang@hebut.edu.cn; wbi@hebut.edu.cn; volkan@

6:07:24

superlattice p-EBL<sup>11</sup> and staircase p-EBL.<sup>12</sup> Recently, the AlGaN/GaN/AlGaN p-EBL with a very thin GaN insertion layer is proposed where the valence subbands in the thin GaN insertion layer can significantly reduce the p-EBL barrier height for holes.<sup>13</sup> The p-EBL blocking effect can also be suppressed by making holes "hot"<sup>14</sup> and/or increasing the hole concentration in the p-GaN layer through a hole modulator.<sup>15</sup> Last but not the least, the hole injection is also substantially impacted by the p<sup>+</sup>-GaN and the p-electrode. Considering the low Mg activation efficiency,<sup>16</sup> it is very difficult to shorten the width of the surface depletion region in the p<sup>+</sup>-GaN layer, and this can cause the negative effect on the hole injection. In this work, we propose a charge inverter by growing a very thin SiO<sub>2</sub> insulator on the p<sup>+</sup>-GaN surface, and the p<sup>+</sup>-GaN surface will present a weak inversion layer when the device is biased. The weak inversion layer can reduce the tunnel region width, and in the meanwhile, compared to the  $p^+$ -GaN, the smaller dielectric constant of the SiO<sub>2</sub> layer also produces a stronger electric field, which can further promote hole injection. Most importantly, such a charge inverter can reduce the forward voltage and increase the quantum efficiency of the LED device. In addition, the charge inverter can be easily fabricated without increasing the fabrication complexity.

FIG. 1. Schematic energy band diagrams (layer thickness not in scale) for (a) device A without the charge inverter and (b) device B with the charge inverter. The carrier transport includes three processes: process 1 means the nonequilibrium electrons (solid circles) travel to the ITO layer from the conduction band of the p<sup>+</sup>-GaN layer, process 2 means the electron interband tunneling which then simultaneously produces the holes (open circles), and the holes will then travel (process 3) to the MQW region. The charge inverter and the inversion layer are also shown in Fig. (b).  $E_C$ ,  $E_V$ ,  $E_{fe}$ , and  $E_{fh}$  represent the conduction band, valence band, quasi-Fermi level for electrons, and quasi-Fermi level for holes, respectively.

ITO tunnel region (PITR). Device B with the charge inverter is demonstrated in Fig. 1(b), from which we can see the inserted insulator between the p<sup>+</sup>-GaN and the ITO layer, and we call this semiconductor-insulator tunnel region (SITR). Under forward-bias, the electrons will tunnel through the PITR and SITR for device A and device B, respectively, and then the holes are left and injected into the MQW region. The advantage of the SITR design is the formation of the weak inversion layer at the p<sup>+</sup>-GaN/insulator interface when the device is forward-biased [see Fig. 1(b)]. The inversion layer is able to attract and confine the electrons at the p<sup>+</sup>-GaN/insulator interface. This can then substantially shorten the width of the tunnel region, which can significantly increase the carrier tunnel efficiency.<sup>17</sup> Meanwhile, if the dielectric constant of the insulator is smaller than the GaN and the ITO layers, the electric field within the tunnel region can also be significantly enhanced, which is very useful to further facilitate the hole injection.

The effectiveness of the charge inverter in improving the LED performance is tested with blue InGaN/GaN LEDs, which were grown by the metal-organic chemical vapor deposition (MOCVD) system. The epi-wafers were initiated on the [0001] oriented planar sapphire substrate. We first grew the 20 nm thick GaN nucleation layer followed by the 4  $\mu$ m thick unintentionally n-type GaN layer (u-GaN). The  $2 \mu m$ n-GaN layer with the Si doping concentration of  $5\times 10^{18} \text{cm}^{-3}$  was achieved by the diluted SiH\_4 precursor. Then, we grew the five-period In<sub>0.15</sub>Ga<sub>0.85</sub>N/GaN MQW stack in which the quantum well and the quantum barrier is 3 nm and 12 nm thick, respectively. We did not adopt any intentional dopants in the quantum barriers. The MQWs were then capped by the 25 nm thick p-Al<sub>0.20</sub>Ga<sub>0.80</sub>N EBL structure to better confine the electrons. The holes are provided by the p-GaN layer, which was grown after the p-EBL. The thickness of the p-GaN layer is  $0.2 \,\mu\text{m}$ . The p-type conductivity was realized by doping the epi-wafer with Mg dopants. We assume 1% as the ionization ratio for the Mg dopants, and the effective hole concentration in the p-EBL and the p-GaN layer is estimated to be  $3 \times 10^{17}$  cm<sup>-3</sup>. We also grew the heavily Mg doped GaN layer (p<sup>+</sup>-GaN) with the 20 nm thickness to enable the ohmic contact. The whole epi-wafers were finally *in situ* annealed (600 s at the temperature of 720 °C) in the N<sub>2</sub> atmosphere.

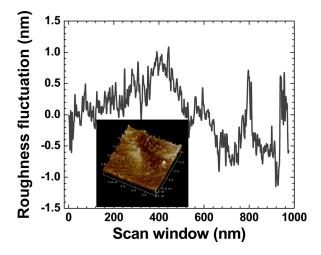

After the epitaxial growth, we measured the surface roughness of the p<sup>+</sup>-GaN layer for the LED epi-wafer by the Atomic Force Microscope (AFM). The size of the scanned window is  $1 \times 1 \mu m^2$ , and the scan rate is set to 1 Hz. The surface morphology for the tested LED is presented in Fig. 2, from which we can see that the surface roughness fluctuation is smaller than 1 nm. Therefore, in order to obtain the continuous film while not causing significant current blocking effect, we tentatively deposited an insulation layer as thin as 1 nm on the p<sup>+</sup>-GaN surface.

The LED wafers were then fabricated by following the standard fabrication process. The LED epi-wafers were patterned into a mesa of  $350 \times 350 \,\mu\text{m}^2$  by the reactive ion etch

FIG. 2. The AFM image and surface roughness of the p<sup>+</sup>-GaN layer for a complete InGaN/GaN MQW LED before depositing the insulation film.

(RIE) technology. For device A, we formed the ITO layer on the p<sup>+</sup>-GaN layer by E-beam and the ITO layer thickness was 50 nm. For device B, before depositing the 50 nm thick ITO layer, we first grew a thin SiO<sub>2</sub> layer at 300 °C on the p<sup>+</sup>-GaN surface, and the SiO<sub>2</sub> layer was obtained by optimizing the PECVD system and the thickness was set to ~1 nm. The thin SiO<sub>2</sub> layer was patterned and wet etched by using the diluted HF acid. Then, for both devices, the ITO layer was annealed in the ambient of N<sub>2</sub>:O<sub>2</sub> (4:1) at the temperature of 630 °C for 1 min. We finally deposited the Ti/Au (30 nm/100 nm) metal stack on both the ITO surface and the n-GaN surface to form the p-electrode and the n-electrode.

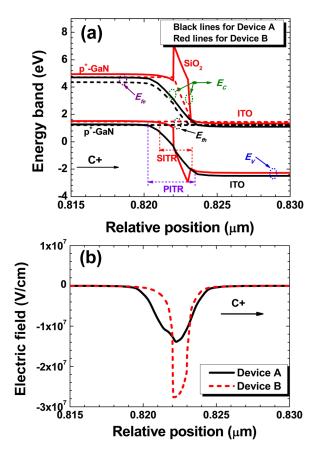

We calculated the energy band diagrams [see Fig. 3(a), data calculated at 100 mA] in the vicinity of the PITR and the SITR for devices A and B, respectively. The numerical calculations were conducted by APSYS, which is able to solve the Poisson and Schrödinger equations self-consistently with the proper boundary conditions. The carrier transport was modeled by the carrier drift and diffusion processes. Besides the thermionic emission and field emission, we also considered the interband tunneling for the PITR and the SITR if we treat the ITO layer as the heavily doped n-type semiconductor. The piezoelectric and spontaneous polarization effect was taken into account for the [0001] oriented InGaN/GaN LEDs,<sup>18</sup> and here, we empirically

FIG. 3. Numerically calculated (a) energy band diagrams, (b) electric field profiles for the PITR and SITR at 100 mA. Here,  $E_C$ ,  $E_V$ ,  $E_{fe}$ , and  $E_{fh}$  denote the conduction band, valence band, quasi-Fermi level for electrons, and quasi-Fermi level for holes, respectively. The  $E_{fe}$  in (a) is higher than  $E_C$  at the relative position of 0.8214  $\mu$ m, and this results in the electron accumulation and a reduced tunnel width. The positive direction of the electric field is pointed from the ITO layer to the p<sup>+</sup>-GaN layer.

assumed the 40% polarization level due to the strain release by generating dislocations.<sup>5,14,15</sup> Other important factors such as the band offset for InGaN/GaN and GaN/AlGaN heterostructures, Auger recombination coefficient, and Shockley-Read-Hall recombination can be found in our previous reports.<sup>5,14,15</sup>

Investigations to Fig. 3(a) illustrate that the width of the SITR is substantially reduced compared to that of the PITR. The width of the PITR is  $\sim$ 3.5 nm while the width for the SITR is  $\sim 2 \text{ nm}$ . Note the tunnel region width is defined as the distance between the two points at which the quasi-Fermi level for holes intersects with the valence band of the p<sup>+</sup>-GaN layer and the conduction band of the ITO layer, respectively. The reduced tunnel width of the SITR is well attributed to the charge inverter, which enables the inversion layer at the p<sup>+</sup>-GaN surface. The charge inversion in the SITR is evidenced by the alignment of the quasi-Fermi level  $(E_{fe})$  of electrons and the conduction band  $(E_C)$ . The  $E_{fe}$  overtakes the  $E_C$  in the energy level at the relative position of  $0.8214 \,\mu\text{m}$  for the SITR as demonstrated in Fig. 3(a), and thus, the electrons accumulate at the interface of the p<sup>+</sup>-GaN layer and the SiO<sub>2</sub> insulator. The electron accumulation shrinks the surface depletion in the p<sup>+</sup>-GaN layer, which gives rise to the reduced width of the SITR for LED B. However, due to the lack of the SiO<sub>2</sub> layer, the charge inversion will not happen in the PITR as illustrated in Fig. 3(a). This leads to a wider surface depletion region in the p<sup>+</sup>-GaN layer and makes the interband tunneling efficiency low. Meanwhile, according to our calculations, the width variation of PITR and SITR is negligible at different set biases in this work, which is consistent with the report in Ref. 17. We also show the electric field profiles for the PITR and SITR in Fig. 3(b) at 100 mA. According to Fig. 3(b), the electric field intensity for the SITR is larger than that for PITR, thanks to the lower dielectric constant of the SiO<sub>2</sub> layer ( $\epsilon_r = 3.9$ ) compared to 8.9 of the p<sup>+</sup>-GaN layer. The enhanced electric field can better promote the carrier interband tunneling efficiency of the SITR for device B.<sup>17</sup> Note that the SiO<sub>2</sub> layer thickness in the charge inverter has to be optimized and makes it properly thin. If the SiO<sub>2</sub> layer is too thick, the SITR will be significantly widened and this can severely block the hole injection, which leads to a poor quantum efficiency. We shall also pay attention to the dielectric constant ( $\epsilon_r$ ) of the thin insulator layer in the charge inverter, and a  $\epsilon_r$  as low as possible is required to achieve the high electric field magnitude in the tunnel region.

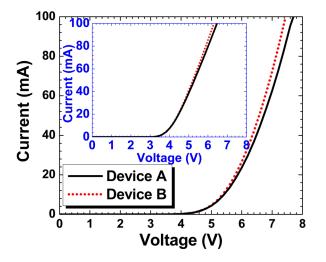

We measured and calculated the device current in terms of the applied voltage (I-V) for the fabricated devices, which is presented in Fig. 4. We can see that the forward voltage of device B is smaller than that of device A, and this is ascribed to the facilitated hole injection efficiency from the p-electrode into the  $p^+$ -GaN layer for device B. Meanwhile, the increased electric field in the thin SiO<sub>2</sub> layer also enables a more smooth hole transport and improves the injected current. Note the experimentally measured forward voltage for both devices can be further reduced if the thermal annealing condition for the ITO layer is fully optimized.

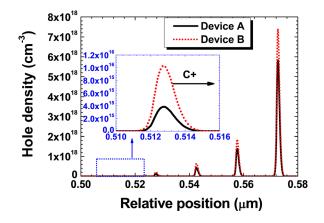

The numerically calculated hole density profiles are illustrated in Fig. 5. Clearly, we can observe that the hole concentration in the quantum wells for device B is higher

FIG. 4. Experimentally measured current-voltage characteristics for devices A and B. Inset shows the numerically calculated current-voltage characteristics for devices A and B.

than that for device A. As has been mentioned earlier, the charge inverter helps to reduce the width of the tunnel junction, and the SiO<sub>2</sub> layer with a lower  $\epsilon_r$  increases the electric field intensity, which result in the enhanced hole transport from the p-electrode to the p<sup>+</sup>-GaN layer, and this simultaneously increases the hole injection efficiency into the quantum wells. Since the quantum barriers in the proposed device is not engineered in the way of favoring the uniform hole distribution in the MQW region, we see the lowest hole concentration in the quantum barriers can be more homogeneously distributed by, e.g., employing the InGaN as the quantum barriers.<sup>6</sup>

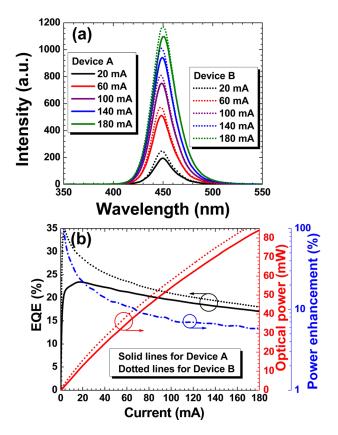

The impact of the charge inverter is justified by measuring the optical performance for devices A and B as shown in Figs. 6(a) and 6(b), respectively. Fig. 6(a) presents the electroluminescence (EL) spectra for the two devices, for both of which the peak emission wavelength is 450 nm. Device B produces stronger EL intensity compared to device A within the tested current range. Note that, as the injection current increases, the peak emission wavelengths for both devices slightly show the blue shift that is due to the polarization screening in the quantum wells by the injected

FIG. 5. Hole density profiles for devices A and B at the injection current level of 100 mA.

FIG. 6. Experimentally measured (a) EL spectra, (b) EQE, optical power and the power enhancement at different injection current levels for devices A and B. The mesa size for the tested devices is  $350 \times 350 \,\mu \text{m}^2$ .

carriers, and then show the red shift that is caused by the self-heating effect. We also show the EQE and the optical power as a function of the injected current for both devices A and B in Fig. 6(b). We can see that device B has both higher EQE and optical power than device A, thanks to the promoted hole injection efficiency enabled by the charge inverter. For example, the EQE is increased by 20% at the injection current level of 20 mA for the  $350 \times 350 \,\mu\text{m}^2$  LED chip. However, if the current is further increased to 180 mA, the power enhancement for device B becomes less obvious, and the efficiency enhancement is smaller than 10%, such that though device B can increase the EQE, the efficiency droop is less improved, which is, for example, 27.6% for device A and 48.6% for device B at 100 mA. The observed efficiency droop for device B is likely due to the electron leakage caused by the inversion layer at the p<sup>+</sup>-GaN/SiO<sub>2</sub> interface, given that more nonequilibrium holes are produced at the  $p^+$ -GaN/SiO<sub>2</sub> interface and the inversion layer occurs, which attract more electrons to bypass the MQW region. Thus, more efforts are necessary to optimize the electron injection layer and/or the p-EBL so that both the efficiency enhancement and the reduced efficiency droop can be obtained.

To summarize, in this work, we have reported a charge inverter for III-nitride LEDs. The effectiveness of the charge inverter is probed both numerically and experimentally by growing and fabricating the blue InGaN/GaN LEDs. The studies show that the charge inverter can reduce the width of the tunnel region by forming an inversion layer at the  $p^+$ -GaN surface. By adopting the insulator with a lower

Reuse of AIP Publishing content is subject to the terms at: https://publishing.aip.org/authors/rights-and-permissions. Download to IP: 139.179.65.117 On: Mon, 04 Apr 201

dielectric constant (e.g., SiO<sub>2</sub>), the electric field in the tunnel region can also be increased, which further promotes the hole injection. For that reason, the external quantum efficiency for the proposed LED device that has the mesa area of  $350 \times 350 \,\mu\text{m}^2$  is increased by 20% at 20 mA. Although the efficiency droop caused by electron leakage for the proposed device with the charge inverter is observed, one can minimize the electron leakage by increasing the blocking effect of the p-EBL, adopting the electron cooler and/or the n-EBL to reduce the thermal energy of electrons.<sup>19–22</sup> The charge inverter provides an easy way to enhance the hole injection and increase the quantum efficiency, and we believe it is especially promising for the UV LEDs which use p-AlGaN to provide the hole conduction, since compared to the p<sup>+</sup>-GaN layer, the p<sup>+</sup>-AlGaN layer can have a even larger surface depletion region.

This work was supported by Natural Science Foundation of China (Project No. 51502074).

- <sup>1</sup>S. T. Tan, X. W. Sun, H. V. Demir, and S. P. DenBaars, IEEE Photonics J. 4, 613 (2012).

- <sup>2</sup>G. Verzellesi, D. Saguatti, M. Meneghini, F. Bertazzi, M. Goano, G. Meneghesso, and E. Zanoni, J. Appl. Phys. **114**, 071101 (2013).

- <sup>3</sup>J. Cho, E. F. Schubert, and J. K. Kim, Laser Photonics Rev. 7, 408 (2013).

- <sup>4</sup>Y. Ji, Z.-H. Zhang, S. T. Tan, Z. G. Ju, Z. Kyaw, N. Hasanov, W. Liu, X. W. Sun, and H. V. Demir, Opt. Lett. **38**, 202 (2013).

- <sup>5</sup>Z.-H. Zhang, S. T. Tan, Y. Ji, W. Liu, Z. Ju, Z. Kyaw, X. W. Sun, and H. V. Demir, Opt. Express **21**, 15676 (2013).

- <sup>6</sup>K. Zhou, M. Ikeda, J. Liu, S. Zhang, D. Li, L. Zhang, J. Cai, H. Wang, H.

- B. Wang, and H. Yang, Appl. Phys. Lett. 105, 173510 (2014).

- <sup>7</sup>X. Ni, Q. Fan, R. Shimada, Ü. Özgür, and H. Morkoç, Appl. Phys. Lett. **93**, 171113 (2008).

- <sup>8</sup>C. H. Wang, S. P. Chang, W. T. Chang, J. C. Li, Y. S. Lu, Z. Y. Li, H. C. Yang, H. C. Kuo, T. C. Lu, and S. C. Wang, Appl. Phys. Lett. **97**, 181101 (2010).

- <sup>9</sup>J. Piprek, Appl. Phys. Lett. **104**, 051118 (2014).

- <sup>10</sup>S.-H. Han, D.-Y. Lee, S.-J. Lee, C.-Y. Cho, M.-K. Kwon, S. P. Lee, D. Y. Noh, D.-J. Kim, Y. C. Kim, and S.-J. Park, Appl. Phys. Lett. **94**, 231123 (2009).

- <sup>11</sup>J. H. Park, D. Yeong Kim, S. Hwang, D. Meyaard, E. Fred Schubert, Y. Dae Han, J. Won Choi, J. Cho, and J. Kyu Kim, Appl. Phys. Lett. **103**, 061104 (2013).

- <sup>12</sup>S.-J. Chang, S.-F. Yu, R.-M. Lin, S. Li, T.-H. Chiang, S.-P. Chang, and C.-H. Chen, IEEE Photonics Technol. Lett. 24, 1737 (2012).

- <sup>13</sup>Z.-H. Zhang, Z. Ju, W. Liu, S. T. Tan, Y. Ji, Z. Kyaw, X. Zhang, N. Hasanov, X. W. Sun, and H. V. Demir, Opt. Lett. **39**, 2483 (2014).

- <sup>14</sup>Z.-H. Zhang, W. Liu, S. T. Tan, Y. Ji, L. Wang, B. Zhu, Y. Zhang, S. Lu, X. Zhang, N. Hasanov, X. W. Sun, and H. V. Demir, Appl. Phys. Lett. **105**, 153503 (2014).

- <sup>15</sup>Z.-H. Zhang, Z. Kyaw, W. Liu, Y. Ji, L. C. Wang, S. T. Tan, X. W. Sun, and H. V. Demir, Appl. Phys. Lett. **106**, 063501 (2015).

- <sup>16</sup>S. Nakamura, T. Mukai, M. Senoh, and N. Iwasa, Jpn. J. Appl. Phys., Part 2 31, L139 (1992).

- <sup>17</sup>S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. (Wiley, 1981).

- <sup>18</sup>V. Fiorentini, F. Bernardini, and O. Ambacher, Appl. Phys. Lett. **80**, 1204 (2002).

- <sup>19</sup>Z.-H. Zhang, W. Liu, S. T. Tan, Z. Ju, Y. Ji, Z. Kyaw, X. Zhang, N. Hasanov, B. Zhu, S. Lu, Y. Zhang, X. W. Sun, and H. V. Demir, Opt. Express 22, A779 (2014).

- <sup>20</sup>Z.-H. Zhang, Y. Ji, W. Liu, S. Tiam Tan, Z. Kyaw, Z. Ju, X. Zhang, N. Hasanov, S. Lu, Y. Zhang, B. Zhu, X. Wei Sun, and H. V. Demir, Appl. Phys. Lett. **104**, 073511 (2014).

- <sup>21</sup>F. Zhang, X. Li, S. Hafiz, S. Okur, V. Avrutin, Ü. Özgür, H. Morkoç, and A. Matulionis, Appl. Phys. Lett. **103**, 051122 (2013).

- <sup>22</sup>X. Ni, X. Li, J. Lee, S. Liu, V. Avrutin, Ü. Özgür, H. Morkoç, A. Matulionis, T. Paskova, G. Mulholland, and K. R. Evans, Appl. Phys. Lett. **97**, 031110 (2010).